- 頭條多電壓與掃描鏈技術在芯片設計中的應用2021-08-17 作者:向韜鑫 王仁平 等 | 來源:《電氣技術》 | 點擊率:導語針對芯片中功耗高、測試成本較高的問題,福州大學物理與信息工程學院的研究人員向韜鑫、王仁平、劉東明、陳榮林,在2020年第6期《電氣技術》雜志上撰文,以一款乘加器為例,該乘加器可以切換在乘、加、乘加3種工作狀態。在芯片設計過程中,利用統一標準格式技術實現多電壓設計達到低功耗的效果,利用掃描鏈技術,完成可測試性設計,降低芯片的測試成本,并解決了兩種技術的兼容性問題。

5G通信和物聯網時代即將到來,各類芯片不斷高性能化,設計規模也不斷變大。而近年逐漸失效的摩爾定理,很難使芯片的價格和工藝尺寸同時減小,因此在實現高性能的同時,節約功耗和降低生產成本越來越受關注。對于數字信號處理芯片,乘、加、乘加算法都是其較為常見的運算模塊,將3種算法整合在一起,并使其可以自由切換工作狀態,能較大地節省面積成本。

除此之外,低功耗技術設計和可測試性設計(desgin for test, DFT)技術也可以降低芯片功耗成本和測試成本。利用統一標準格式(unified power format, UPF)實現多電壓技術。根據不同模塊性能需求,在芯片內劃分不同的電壓域(power domain)進行分割處理,實現低功耗設計。

而DFT中的掃描鏈技術(scan chain)可以在短時間內檢查芯片內部各寄存器的好壞,早一步將因工藝缺陷和塵埃附著的損壞芯片在裸片階段檢測出來,可以防止損壞的芯片流入下一階段的設計中而造成更大損失。

1 電路設計

1.1 電路邏輯設計

加、乘、乘加是數字處理芯片常見的3種算法,但芯片內3種算法都在滿負荷同時工作的狀態中的情況并不多見,因此在芯片中插入一些可切換狀態,并整合了3種功能的乘加器,隨芯片的工作需要,調整芯片的工作狀態,可以節省面積。

本設計中以二輸入的mode信號作為控制信號,mode信號通過控制數據選擇器,來控制在各模塊輸入和頂層輸出端的采樣,最終來控制乘加器工作狀態,如圖1所示。

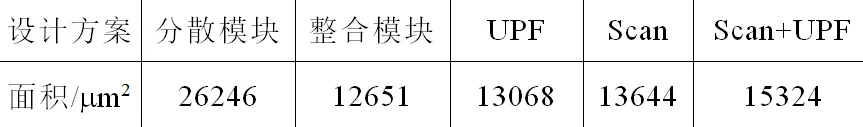

輸入mode分別在00、01、10、11時,乘加器分別切換到乘、加、乘加、關閉的工作狀態。除此之外mode信號還控制著電源控制模塊的狀態,完成多電壓控制。乘加器設計在200M頻率下工作,在SMIC55nm工藝下,不同設計方案的模塊綜合面積見表1。其中分散模塊指3種運算模塊分開設計,并同時存在于設計中。

圖1 多狀態乘加器結構圖

表1 不同設計方案的綜合面積比較

本次設計的32位乘加器共分為4個步驟:

1)編寫Verilog語言及Testbech完成電路邏輯設計實現仿真。

2)利用Synopsys的邏輯綜合(design compiler, DC)的拓補模式將寄存器傳輸級(register transfer level, RTL)verilog代碼轉換為門級電路,同時插入UPF和scan chain分別對乘加器的電壓供電情況和掃描鏈進行描述,并利用TetraMAX生成測試向量。

3)利用Synopsy的集成電路布局布線工具(integrated circuit compiler, ICC),最終生成GDS格式的版圖。

4)利用Primerail對生成的版圖進行功耗測試。

1.2 多電壓綜合

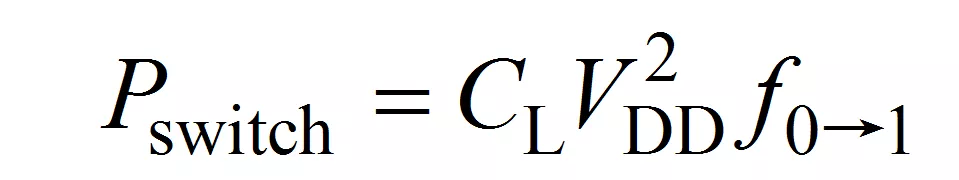

多電壓設計,利用了UPF,其現在已經成為IEEE- 1801標準且為國際三大電子設計自動化(electro- nics design automation, EDA)廠商均支持的標準。在此使用UPF技術描述設計電路的電壓工作狀態,分別降低動態和靜態功耗:

1)降低動態功耗

將需要資源需求較大的乘法劃為高電壓的電壓域PDM,將在對于資源要求一般的加法器劃為低電壓的電壓域PDA,其余模塊會被EDA工具默認置入頂層模塊所在低電壓的PDT電壓域,使不同性能需求的模塊分別在高低電壓下工作,從而降低動態功耗(dynamic power)。由于PDT和PDM的電壓不同,因此還需對它們之間的輸入輸出信號插入電平轉換單元(level-shifter),如圖2所示。動態功耗的主要消耗為開關功耗。

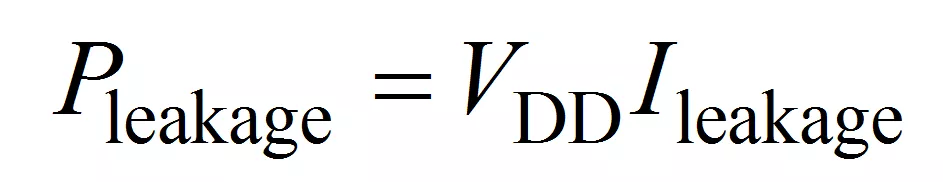

公式1

圖2 乘加器模塊電壓域圖

2)降低靜態功耗

要降低靜態功耗可以在模塊處于非工作狀態時對其進行關斷。這里需要插入和替換各種多電壓器件:①電源開關將電壓域的主電源關閉或打開;②保留寄存器可以在主電源關閉時以備用電源供電,以保留斷電之前的數據;③隔離單元用于將關閉的電壓域的數據進行穩定輸出,防止不定態輸出。

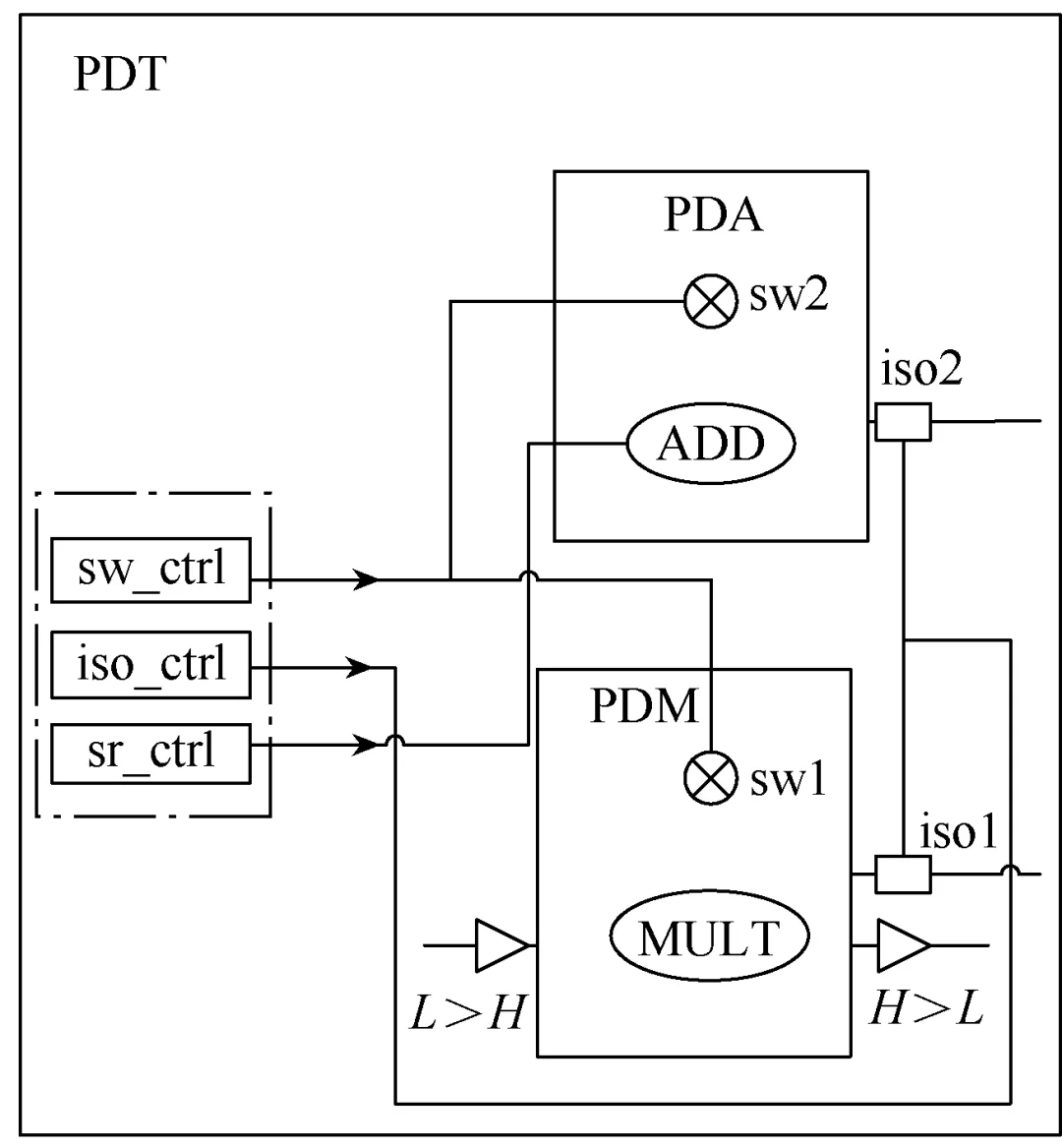

在RTL設計中電源控制模塊控制著他們的工作狀態,如圖2所示,虛框內為電源控制模塊。當一個模塊要關斷時,sr_crtl信號會先將保留寄存器切換至save狀態以保存住這些寄存器的現時數據,并隨后sw_crtl信號關閉電源開關,iso_crtl信號打開隔離單元承擔數據的輸出。

若要重新打開一個電壓域,其保留寄存器要在電源開關開啟后換至restore狀態,讀取斷電前被保存的數據。最終,乘加器模塊通過合理地開關各電壓閾最終達到降低靜態功耗(leakage power)的目的。

公式 2

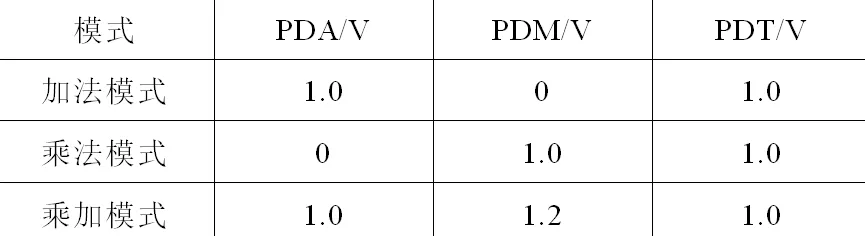

設計好各電壓域工作狀態后,還需建立電源狀態表定義不同狀態的各電壓域工作電壓,見表2,本次設計采用了多角多模(multi corner multi mode, MCMM)模型,為了驗證不同電壓下的工作情況,除了表中標出的電壓外,還添加了上下兩個相差10%的電壓,以確保芯片在這些不同電壓下均可以正常工作。

表2 乘加器電源狀態表

1.3 電源控制模塊封裝掃描

掃描鏈測試的掃描方法實際上就是將各觸發器加上一個數據選擇器,使其擁有兩個模式。第一個為正常模式,在正常模式下,所有的寄存器如同往常一樣工作。另一種為掃描測試模式,實質上就是將觸發器連接成多個移位寄存器,稱為掃描寄存器。

在測試模式下,掃描時鐘控制掃描寄存器,捕獲輸出信號后比對數據以檢測寄存器是否正常工作,這樣較大節省了測試時間和成本。

但與普通的可測試性設計不同,因為多電壓設計中含有普通設計中沒有的隔離單元,保留寄存器,電源開關,它們的工作狀態均受信號的控制。但在掃描模式下,所有的寄存器的輸出值均是由掃描信號掃描輸入的,而與其在功能模式下正常工作不同,受控的保留寄存器和隔離單元會產生信號錯亂,這些錯誤的信號控制著這些多電壓器件工作狀態,最終導致整個芯片在掃描模式下全部混亂。

因此在掃描鏈設計時,電源控制模塊的掃描鏈需要單獨設計。在此對兩種不同的信號控制方法,一種外部輸入并直接控制,另一種為信號控制模塊在芯片內部,對二者掃描鏈設計有兩種不同的設計方案。

1)信號由外部輸入時

可以將外部輸入的多電壓控制信號設置為Constant模式,將信號固定在0或1值,這樣就使各種多電壓等在DFT測試階段均不做信號改變的動作,再按常規步驟對剩余電路進行掃描鏈設計。

2)電源控制模組在芯片內部

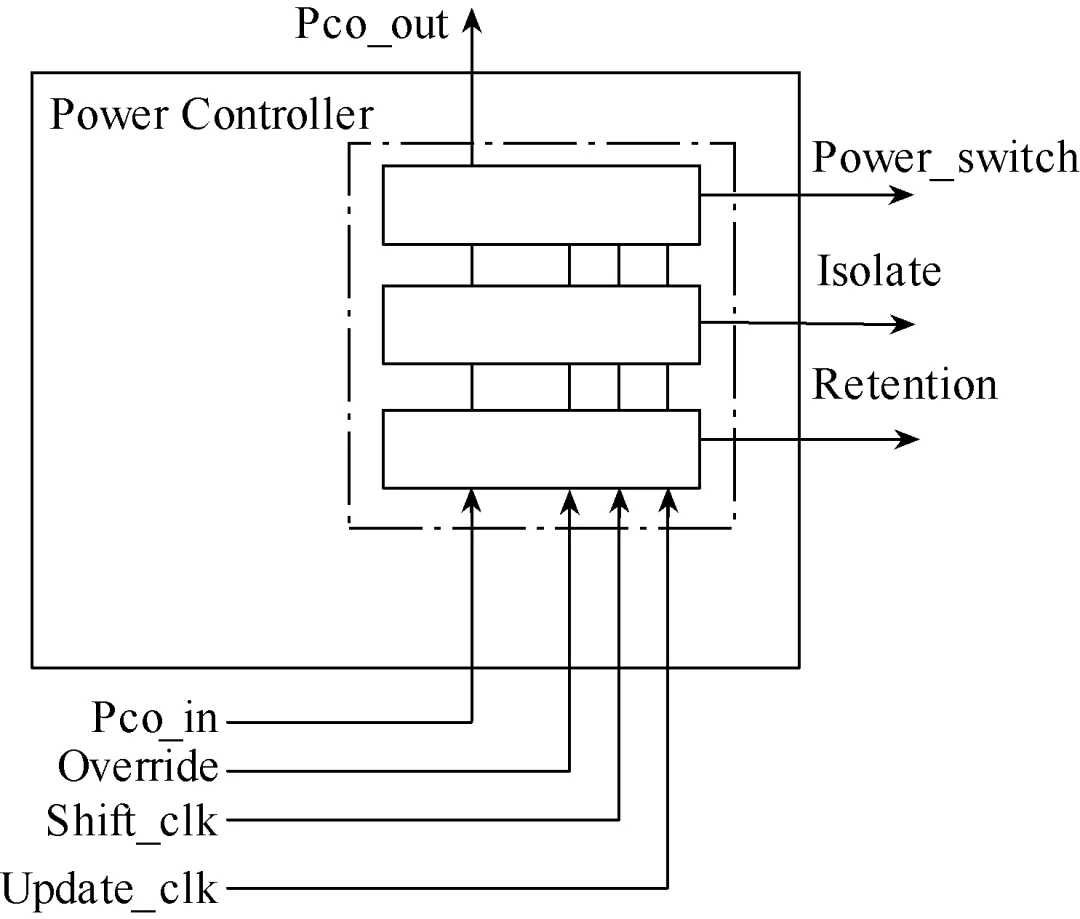

如本設計,若電源控制模組在芯片內部時,如果將其模塊的控制信號輸出值固定,這樣雖然不會打亂受控多電壓器件的工作狀態,但是也無法對電源控制模組進行掃描測試。因此需要將內部的電源控制模塊單獨封裝為一個封裝掃描鏈,進行測試,如圖3所示。

圖3 電源控制模塊封裝掃描鏈設計圖

其原理其實就是將電源控制模塊的輸出部分封裝,并與芯片內其余的掃描鏈分開,形成一條單獨的掃描鏈,并且此掃描鏈的時鐘也不是其余掃描鏈模塊共用的掃描時鐘,而是一個單獨時鐘shift_clk,并由update_clk和override信號的組合控制使其控制的多電壓器件可以正常工作。最終實現對整個芯片各個模塊的測試覆蓋,并且不會產生信號混亂的問題。

但這條特殊的掃描鏈不能與其余掃描鏈壓縮在一起,所以需要單獨的掃描IO端口。但對于乘加器模塊來說,其IO端口多達幾十個,在掃描模式中,不用從功能模塊的IO端口中輸入輸出。因此在掃描鏈設計時,各種額外的端口可以借用功能模式下的IO端口,利用一個數據選擇器進行復用,這樣可以節省IO端口的使用,從而也可以節省芯片的面積。

使用TetraMAX軟件,對插入掃描鏈后的電路進行自動測試向量生成。運行結果表明,掃描測試的測試覆蓋率為96.8%,滿足設計要求。生成的測試向量將在芯片生產后供測試使用。

1.4 物理設計

將插入綜合好的verilog、UPF、scan_def和sdc格式的文件分別讀入ICC后,對其進行數字版圖設計。在整體布局上,由左輸入,由右輸出,輸出數據先經頂層模塊到乘法器模塊,再連接加法器模塊,最后由輸出端口輸出。

除了常規的數字版圖流程外,還要創建voltage area與在UPF定義的power domain的對應。前者是在物理設計中真實存在的電壓區域,需要定義大小、高度、位置,而后者則僅僅是對其電壓模塊的邏輯電壓定義。

在此voltage的區域與乘法器模塊區域完全重疊。多電壓器件的電源開關也要在物理設計確定具體的位置,而不是由工具自動擺放,因此要確保需要關斷的電壓域PDA和PDM內每個標準單元的主供電電源都連接到電源開關。

乘加器模塊的供電方式采用了電源環外圍供電與電源網格供電,供電電壓分別為高(1.1~1.32V)、低(0.9~1.08V)、地(0V)3個電壓,其中乘法器模塊工作在高電壓的工作模式下,整體布局圖如圖4所示。再經自動布局布線(place and route, P&R)過程后最終生成GDS版圖。

圖4 多狀態乘加器物理設計布局圖

2 功耗分析

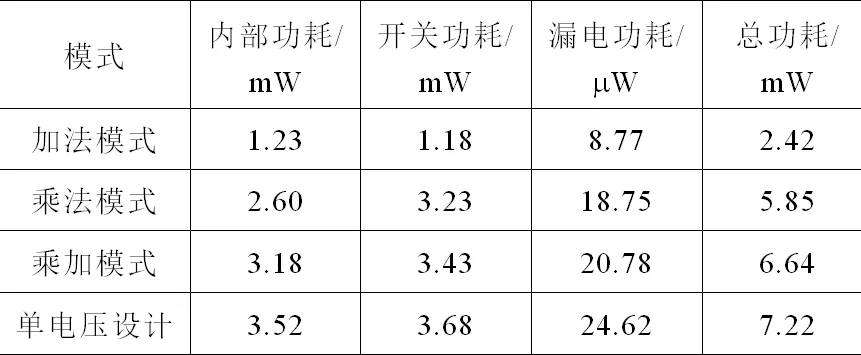

乘加器設計在200M頻率下工作,乘法器工作在1.08V,加法器工作在0.9V時,利用Primerail工具進行評估,并調用SMIC55nm工藝庫標準單元,其布局后功耗見表3。

表3 不同模式功耗消耗

由表3可見,在多電壓設計下,芯片運行在全負荷的乘加模式仍比單電壓設計節省功耗8.0%,除此外,多電壓設計還可以根據需要對不同模塊按需進行開啟和關斷,更徹底地降低功耗。

3 結論

本文簡述了多電壓設計與掃描鏈設計在一個可以切換工作狀態的32×32乘加器設計同時應用的方案。該方案結合了UPF和scan chain技術的概念及使用。

前者可以對不需要工作的模塊進行電源關斷降低靜態功耗,及將不同性能的模塊分高低電壓處理降低動態功耗;后者可以實現在裸片時對芯片進行測試驗證其好壞。兩種技術可以在犧牲較小的面積的前提下同時實現。

電廠關鍵技術研究及其應用”專題征稿通知.jpg)