- 頭條《電工技術學報》優秀論文|抑制SiC MOSFET橋臂串擾的改進門極驅動設計2021-12-10 作者:李輝 黃樟堅 等 | 來源:《電工技術學報》 | 點擊率:導語傳統驅動下SiC MOSFET受高開關速度特性及寄生參數影響,橋臂串擾現象更加嚴重,而現有抑制串擾驅動電路又會增加開關損耗、開關延時和控制復雜程度,本文結合驅動阻抗控制與負壓關斷的串擾抑制方法,提出一種改進門機驅動電路。試驗結果表明,相比典型抑制串擾驅動電路,提出的驅動方法在有效抑制串擾的同時,減小了開關損耗與開關延時。

《電工技術學報》2019年度優秀論文獲獎論文簡報

《光伏發電出力預測技術研究綜述》等15篇優秀論文入選《電工技術學報》2019年度優秀論文,榮獲中國電工技術學會表彰。現將部分獲獎論文的文章簡報分享給各位讀者,以期促進本領域的技術交流。

傳統驅動下SiC MOSFET受高開關速度特性及寄生參數影響,橋臂串擾現象更加嚴重,而現有抑制串擾驅動電路又會增加開關損耗、開關延時和控制復雜程度,本文結合驅動阻抗控制與負壓關斷的串擾抑制方法,提出一種改進門機驅動電路。試驗結果表明,相比典型抑制串擾驅動電路,提出的驅動方法在有效抑制串擾的同時,減小了開關損耗與開關延時。

團隊介紹

重慶大學李輝教授研究團隊主要圍繞可再生能源電力裝備安全可靠運行開展研究,擁有完備的材料-封裝-器件-裝備仿真及實驗平臺。近五年,團隊在大功率電力電子器件可靠性研究方向承擔了國家自然科學基金智能電網聯合基金重點項目1項“壓接型IGBT器件封裝老化失效演化機理及測評方法”,參與國家重點研發計劃項目3項“電力系統用國產高壓大功率IGBT芯片及模塊的應用研發”、“碳化硅大功率電力電子器件及應用基礎理論研究”、“大容量電力電子裝備多物理場綜合分析及可靠性評估方法研究”;承擔國家自然基金面上項目2項,參與工信部高新技術科研項目1項,國際合作項目2項以及省部級科技項目10余項;獲重慶市科技進步二等獎、三等獎各1項。

李輝

1973出生,教授,博士生導師,教育部新世紀優秀人才支持計劃入選者,愛思唯爾“中國高被引學者”,輸配電裝備及系統安全國家重點實驗室副主任,中國電機工程學會電力電子器件專業委員會委員,中國工業節能與清潔生產協會綠色電機系統專業委員會專家,IET Renewable Power Generation副編輯。主持國家自然科學基金重點項目1項、面上項目2項,參與國家重點研發計劃項目2項和國際合作項目2項,獲重慶市科技進步二等獎1項(第一完成人),發表高質量學術論文72篇,出版專著1部,授權國家發明專利16件,申請發明專利11件。主要研究方向為電力電子器件封裝與可靠性、風力發電技術、特種電機系統設計與控制。

黃樟堅

1992出生,碩士研究生,研究方向為SiC電力電子器件驅動設計及應用。

研究背景

近年來,以碳化硅(Silicon Carbide, SiC)MOSFET 為代表的寬禁帶半導體器件因其具有高開關頻率、高開關速度、高熱導率等優點,已成為高頻、高溫、高功率密度電力電子變換器的理想選擇。然而隨著SiC MOSFET開關速度加快,橋式電路受寄生參數影響加劇,串擾現象更加嚴重。由于SiC MOSFET 正向閾值電壓與負向安全電壓較小,串擾問題引起的正負向電壓尖峰更容易造成開關管誤導通或柵源極擊穿,進而增加開關損耗,嚴重時損壞開關管。

論文方法及創新點

提出一種在柵源極增加三極管串聯電容新型輔助支路的改進驅動設計方法,該方法具有開關損耗小、延時較短、控制簡單的特點。論文首先闡述串擾現象的產生原理及其典型抑制方法,其次分析改進驅動電路工作原理與關鍵參數設計原則,最后,搭建雙脈沖實驗平臺,對改進驅動電路有效性進行實驗驗證。

改進抑制串擾驅動電路的思想是在串擾產生過程中,通過控制三極管開斷,使三極管串聯電容的輔助支路為米勒電流提供旁路通道,降低柵極驅動回路阻抗,抑制串擾,同時減小輔助支路電容對 SiC MOSFET開關特性的影響,其原理圖與相關開關波形如圖1、圖2所示。

圖1 改進抑制串擾驅動電路

圖2 改進驅動電路相關波形

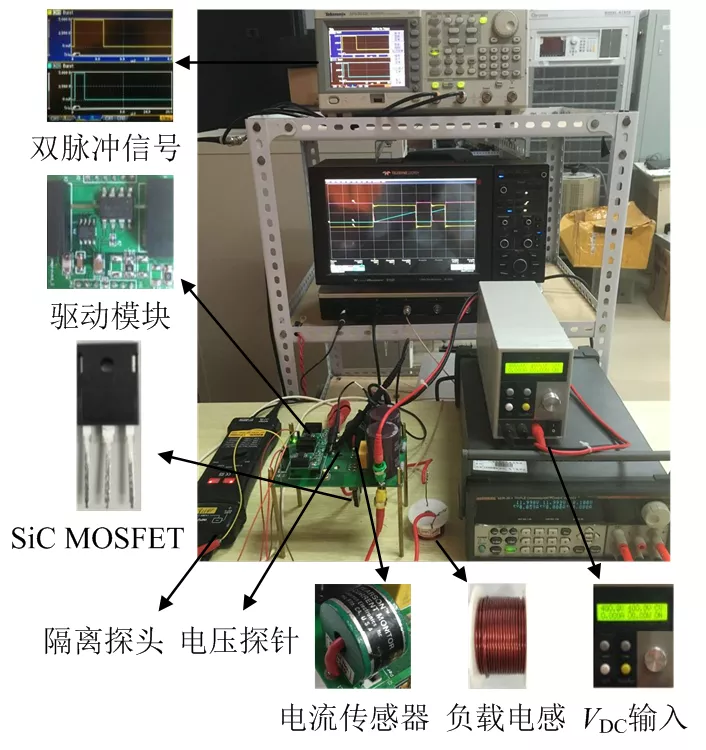

為了驗證改進抑制串擾驅動電路的有效性,本文基于 SiC MOSFET 器件 C2M0080120D,搭建了如圖3所示的雙脈沖測試實驗平臺,并對傳統驅動電路、典型抑制串擾驅動電路、改進抑制串擾驅動電路進行了實驗對比。圖4給出了改進抑制串擾驅動電路原理,圖4~圖6分別給出了驅動電阻為10Ω,輸入電壓為400V,負載電流為5A時,不同驅動電路的實驗波形。

圖3 雙脈沖測試實驗平臺

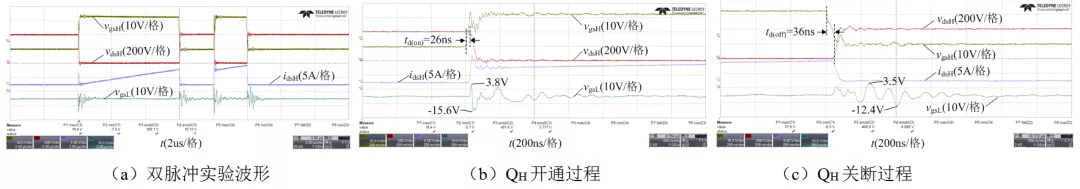

圖4 傳統驅動電路實驗波形

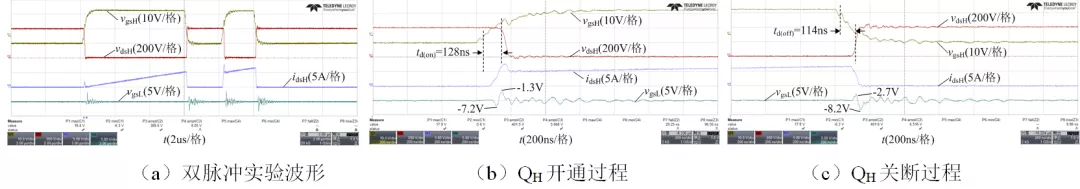

圖5 典型驅動電路實驗波形

圖6 改進驅動電路實驗波形

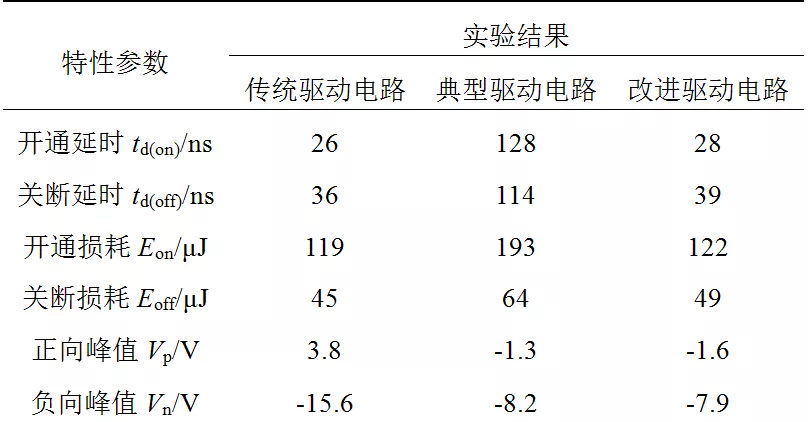

不同驅動電路實驗對比結果如表1所示。

表1 不同驅動電路實驗對比結果

結論

為了有效解決典型驅動電路在抑制串擾同時增加開關延時與開關損耗問題,本文提出了一種在SiC MOSFET柵源極增加三極管串聯電容新型輔助支路的改進抑制串擾驅動電路及其設計方法,并通過原理分析與實驗驗證,表明了所提改進串擾抑制驅動電路及其參數設計方法的有效性。所得主要結論如下:

①傳統無輔助支路的SiC MOSFET驅動電路,橋臂串擾現象明顯。典型抑制串擾驅動和本文所提改進驅動電路都能有效抑制串擾問題。

②無論是典型抑制串擾驅動電路,還是本文提出的改進驅動電路,SiC MOSFET開關損耗都會隨驅動電阻、輸入電壓、負載電流的增大而增加;而SiC MOSFET開關延時受輸入電壓與負載電流影響相對較小,但也會隨驅動電阻的增大而增加。

③相比典型抑制串擾驅動設計,本文所提改進驅動設計有效降低了開關延時與損耗,且隨著驅動電阻、輸入電壓、負載電流增大,降低SiC MOSFET開關損耗的效果更明顯,進一步說明本文所提方法在抑制串擾和提高開關特性方面更具優勢。

引用本文

李輝, 黃樟堅, 廖興林, 鐘懿, 王坤. 一種抑制SiC MOSFET橋臂串擾的改進門極驅動設計[J]. 電工技術學報, 2019, 34(2): 275-285. Li Hui, Huang Zhangjian, Liao Xinglin, Zhong Yi, Wang Kun. An Improved SiC MOSFET Gate Driver Design for Crosstalk Suppression in a Phase-Leg Configuration. Transactions of China Electrotechnical Society, 2019, 34(2): 275-285.

電廠關鍵技術研究及其應用”專題征稿通知.jpg)